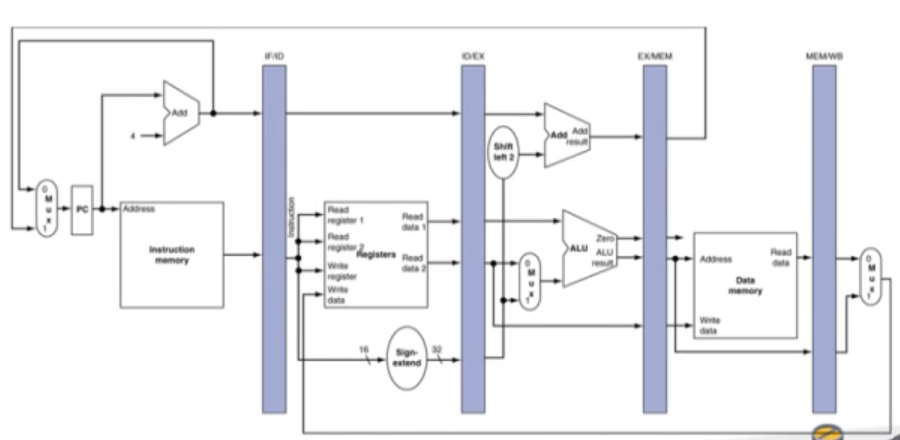

Pieline Register

파이프라인은 각 스테이지에서 나온 값을 저장할 레지스터가 필요. 그래서 각 스테이지 사이에 레지스터를 둠

Single-clock-cycle pipeline diagram

파이프라인이 싱글 사이클일 때, 특정 사이클을 보여줄 때 사용

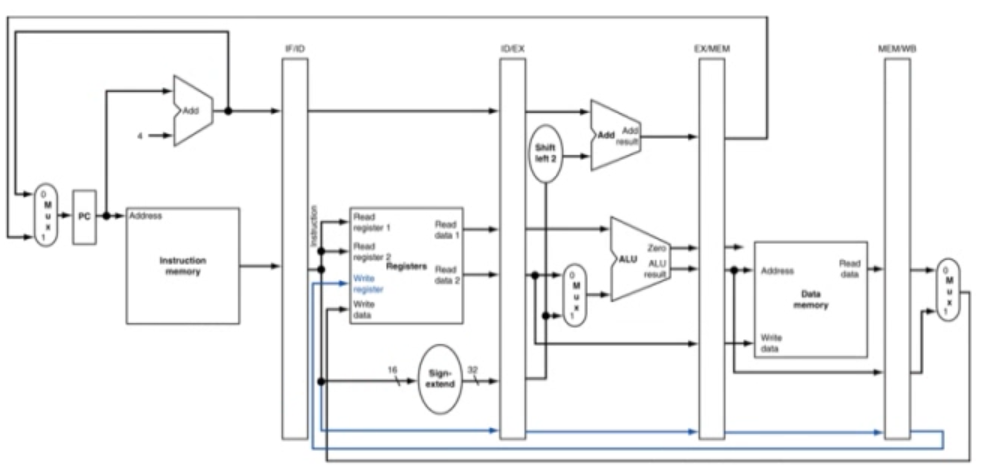

예시) Load 명령어의 파이프라인

기존 Mips의 Pipe에서 Load 명령어를 실행한다면 WB스테이지에서 값을 가져온 후 레지스터로 되돌아온 후, 주소에 값을 저장하게 된다. 하지만 파이프라인을 사용할 시 해당 레지스터에는 다른 명령어의 주소값이 들어가 있게 되므로, 이를 해결하기 위해 load의 datapath(푸른 선)를 추가하여 문제를 해결. dataPath를 추가함으로써 단계가 진행될 때, 같이 데이터가 넘어가는 방식

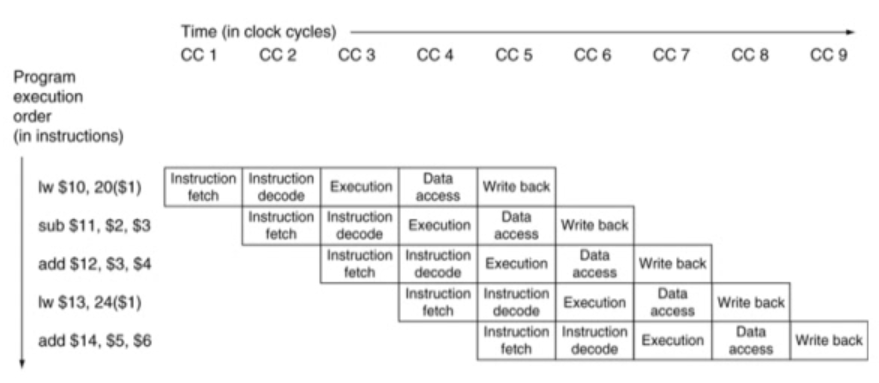

Multi-clock-cycle diagram

여러 사이클의 파이프 라인을 보여 줌

Single-Cycle Pipeline Diagram

특정한 사이클의 파이프라인을 보여줌

현재 예시의 사이클에서는 add, lw, add, sub, lw 총 5개의 명령어가 한 사이클에서 실행되는 상태. 파이프라인은 여러개의 명령어를 pararell 하게 실행시키기에 throughtput(시간당 작업량)을 증가시켜서 성능을 향상함

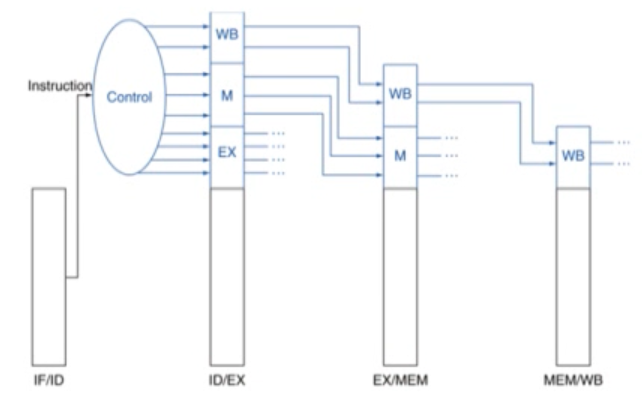

Pipeline Control

각 스테이지에서 다음과 같은 시그널이 필요

ID: RegisterWrite

EX: ALU Resrouce, ALUOP, RegDst

MEM: Branch, MemWrite, MemRead,

WB: MemtoReg

이런 시그널은 ID에서 생성되는데, 이를 각 스테이지 별로 전달하기 위해 PipeLine Control이 사용된다.

따라서 Pipeline의 Control을 포함한 Diagram은 다음과 같이 된다.

'컴퓨터 구조' 카테고리의 다른 글

| Hazard (0) | 2023.09.24 |

|---|---|

| Pipeline의 개념과 성능 (0) | 2023.07.11 |

| ALU Control (0) | 2023.07.11 |

| 프로세서의 명령어 실행 과정 (0) | 2023.07.07 |

| 실수의 표현과 연산 (0) | 2023.07.06 |